- 您现在的位置:买卖IC网 > Sheet目录2001 > ISL12024IVZ (Intersil)IC RTC/CALENDAR EEPROM 8-TSSOP

18

FN6370.3

August 18, 2008

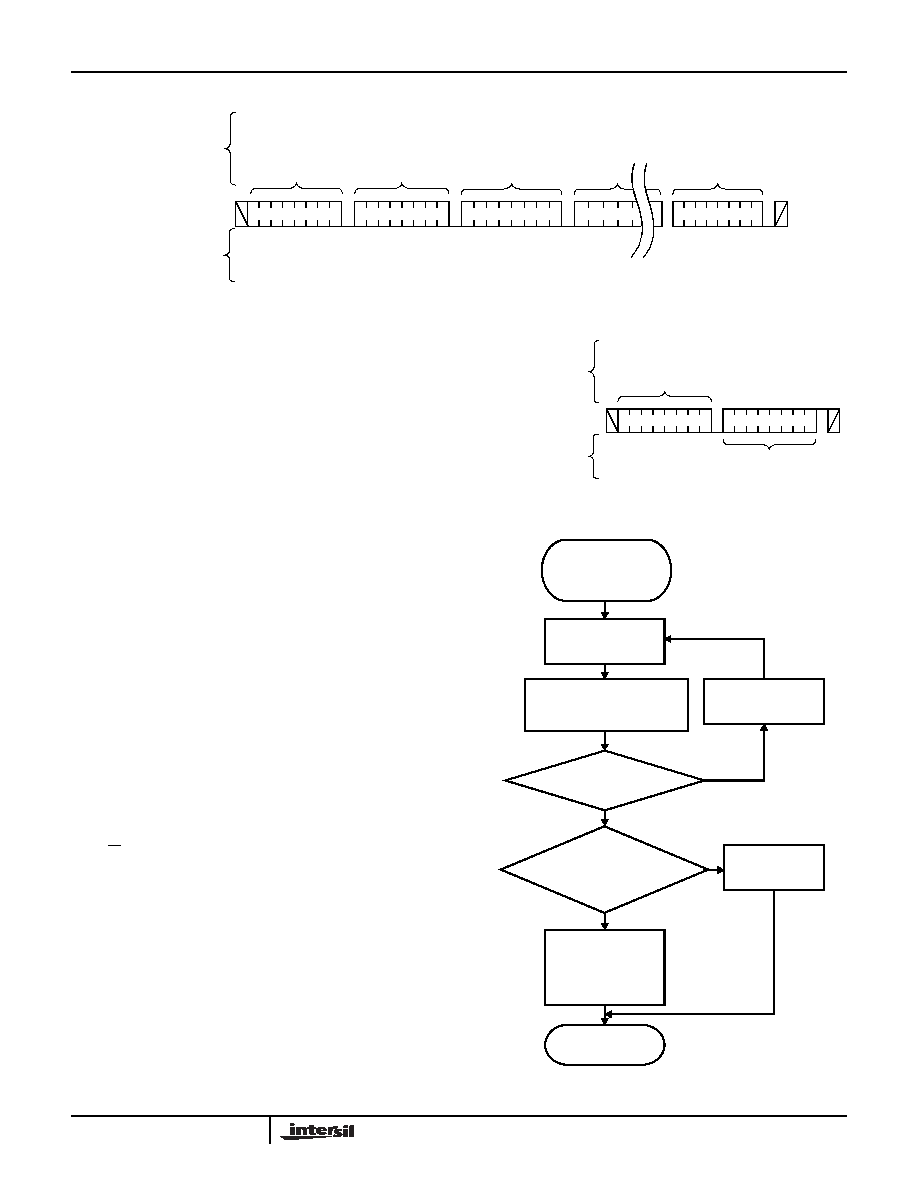

Acknowledge Polling

Disabling of the inputs during non-volatile write cycles can

be used to take advantage of the 12ms (typ) write cycle time.

Once the stop condition is issued to indicate the end of the

master’s byte load operation, the ISL12024 initiates the

internal non-volatile write cycle. Acknowledge polling can

begin immediately. To do this, the master issues a start

condition followed by the Memory Array Slave Address Byte

for a write or read operation (AEh or AFh). If the ISL12024 is

still busy with the non-volatile write cycle, then no ACK will

be returned. When the ISL12024 has completed the write

operation, an ACK is returned and the host can proceed with

the read or write operation. See the flow chart in

Figure 20. Note: Do not use the CCR Slave byte (DEh or

DFh) for Acknowledge Polling.

Read Operations

There are three basic read operations: Current Address

Read, Random Read and Sequential Read.

Current Address Read

Internally the ISL12024 contains an address counter that

maintains the address of the last word read incremented by

one. Therefore, if the last read was to address n, the next

read operation would access data from address n+1. On

power-up, the 16-bit address is initialized to 00h. In this way,

a current address read immediately after the power-on reset

can download the entire contents of memory starting at the

first location. Upon receipt of the Slave Address Byte with

the R/W bit set to one, the ISL12024 issues an

acknowledge, then transmits 8 data bits. The master

terminates the read operation by not responding with an

acknowledge during the ninth clock and issuing a stop

condition. See Figure 19 for the address, acknowledge, and

data transfer sequence.

WORD

ADDRESS 0

S

T

A

R

T

S

T

O

P

SLAVE

ADDRESS

WORD

ADDRESS 1

DATA

(n)

A

C

K

A

C

K

A

C

K

SDA BUS

SIGNALS FROM

THE SLAVE

SIGNALS FROM

THE MASTER

0

DATA

(1)

A

C

K

1

≤ n ≤ 16 for EEPROM ARRAY

1

≤ n ≤ 8 for CCR

1

0 0 00 00 0

FIGURE 18. PAGE WRITE SEQUENCE

S

T

A

R

T

S

T

O

P

SLAVE

ADDRESS

DATA

A

C

K

SDA BUS

SIGNALS FROM

THE SLAVE

SIGNALS FROM

THE MASTER

1

FIGURE 19. CURRENT ADDRESS READ SEQUENCE

ACK

RETURNED?

ISSUE MEMORY ARRAY SLAVE

ADDRESS BYTE

AFH (READ) OR AEH (WRITE)

BYTE LOAD

COMPLETED BY

ISSUING STOP.

ENTER ACK POLLING

ISSUE STOP

ISSUE START

NO

YES

ISSUE STOP

NO

CONTINUE

NORMAL READ OR

WRITE COMMAND

SEQUENCE

PROCEED

YES

NON-VOLATILE WRITE

CYCLE COMPLETE. CONTINUE

COMMAND SEQUENCE?

FIGURE 20. ACKNOWLEDGE POLLING SEQUENCE

ISL12024

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ISL12025IVZ

IC RTC/CALENDAR EEPROM 8-TSSOP

ISL12026IBZ-T7A

IC RTC/CALENDAR EEPROM 8SOIC

ISL12027IV27AZ

IC RTC/CALENDAR EEPROM 8-TSSOP

ISL12028IVZ

IC RTC/CALENDAR EEPROM 14-TSSOP

ISL12029IVZ

IC RTC/CALENDAR EEPROM 14-TSSOP

ISL12030IBZ

IC RTC/CALENDAR EEPROM 8-SOIC

ISL12032IVZ

IC RTC LP BATT BACK SRAM 14TSSOP

ISL12057IUZ

IC RTC/CALENDAR I2C 8-MSOP

相关代理商/技术参数

ISL12024IVZ-T

功能描述:实时时钟 REAL TIME CLK/CLNDR W/EEPROM IN 8LD RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

ISL12025

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Real-Time Clock/Calendar with EEPROM

ISL12025IBZ

功能描述:实时时钟 REAL TIME CLK/CLNDR W/EEPROM 2 63VSET RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

ISL12025IBZ-T

功能描述:实时时钟 REAL TIME CLK/CLNDR W/EEPROM 2 63VSET RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

ISL12025IVZ

功能描述:实时时钟 REAL TIME CLK/CLNDR W/EEPROM 2 63SET 8 RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

ISL12025IVZ-T

功能描述:实时时钟 REAL TIME CLK/CLNDR W/EEPROM 2 63SET 8 RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

ISL12026

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Real Time Clock/Calendar with I2C Bus? and EEPROM

ISL12026_08

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Real Time Clock/Calendar with I2C Bus? and EEPROM